atpg scan test time compression vectors|atpg scan test : online sales We show compression efficiencies allowing a more than 10-fold reduction in tester scan buffer data volume on ATPG compacted tests. In addition, we obtain almost a 2× scan . webEredivisie History, Format, Organization, Media Coverage A Eredivisie (Divisão Principal) é o nível superior do futebol profissional masculino nos Países Baixos. Fundada em 1956 e organizada pela Real Associação Neerlandesa de Futebol (KNVB), a liga opera em um formato de todos contra todos, o que significa que cada equipe joga entre si duas vezes .

{plog:ftitle_list}

O Flashscore.com.br fornece placar ao vivo e resultados finai.

Techniques are presented in this paper that allow for substantial compression of Automatic Test Pattern Generation (ATPG) produced test vectors. We show compression efficiencies .Techniques are presented in this paper that allow for substantial compression of .This question is for testing whether you are a human visitor and to prevent .

This question is for testing whether you are a human visitor and to prevent .

atpg scan test

We show compression efficiencies allowing a more than 10-fold reduction in tester scan buffer data volume on ATPG compacted tests. In addition, we obtain almost a 2× scan .The simplest approach is to perform ATPG for RPR faults not detected by pseudorandom BIST to obtain a set of deterministic test patterns that “top up” the fault coverage to the desired level, . The relationships between a single vendor�s ATPG, the test vector compression/expansion, the scan chain fan-out, and the compactor design rely on thousands of small, proprietary.Complexity of Automotive System-on-Chips is dramatically rising due to the demand for new efficient features in next-generation vehicles. The rising complexity leads to an abnormous .

Scan and ATPG. Scan is the internal modification of the design’s circuitry to increase its test-ability. ATPG stands for Automatic Test Pattern Generation; as the name suggests, this is basically the generation of test patterns.In this paper, we propose a novel and efficient compression-aware ATPG method to significantly boost the performance of ATPG and reduce pattern count. The proposed approach first .Rapidly increasing ASIC gate counts are stressing the test capacity of manufacturing test equipment. New on-product multiple-input signature register (OPMISR) techniques compress .

When an ATPG tool generates a test for a fault, or a set of faults, only a small percentage of scan cells need to take specific values. The rest of the scan chain is don't care, and are usually .Total scan test length: (n comb + 2) n sff + ncomb + 4 clock periods. Example: 2,000 scan flip-flops, 500 comb. vectors, total scan test length ~ 106 clocks. Multiple scan registers reduce test length. Scan Compression. To reduce the test application time (TAT), a single, long scan chain can be broken into N smaller chains, assuming there are sufficient I/O pins available.

The remarkable growth of the circuit size and complexity is primarily due to the advances of VLSI design and manufacturing technologies. The on-chip linear sequential test compression has become the de facto industrial mainstream DFT methodology in reducing the overall cost of testing large chips. In this paper, we propose a novel and efficient compression-aware ATPG . The effectiveness of the ATPG is measured primarily by the fault coverage achieved and the cost of performing the test (algorithm complexity and test length). Benefits of ATPG. The following are the benefits of ATPG that made it popular in the EDA industry. Generates high-coverage test patterns; Lowers test time and cost; Reduce Human efforts

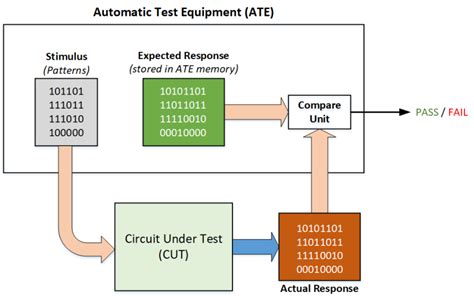

(ATPG-generated) test set to the circuit under test (CUT). Survey of Test Vector Compression Techniques Test data compression consists of test vector compression on the input side and response compaction on the output side. Test vector compression has been an active area of research, yielding a wide variety of techniques. This 63).How the test data valume and tester time reduction happens with compression? 64).what are advantages of modular atpg? 65).How DFT vectors are different from Functional vectors? PDF | In this paper we propose a new method of test patterns compression based on a design of a dedicated SAT-based ATPG (Automatic Test Pattern. | Find, read and cite all the research you need .

Many designs do not connect up every register into a scan chain. This is called partial scan. To enable automatic test pattern generation (ATPG) software to create the test patterns, fault models are defined that predict the expected behaviors (response) from the IC when defects are present. The ATPG tool then uses the fault models to determine .Test compression is a technique used to reduce the time and cost of testing integrated circuits.The first ICs were tested with test vectors created by hand. It proved very difficult to get good coverage of potential faults, so Design for testability (DFT) based on scan and automatic test pattern generation (ATPG) were developed to explicitly test each gate and path in a design.

The test data volume increases exponentially with increase in circuit size. For large circuits, the growing test data volume causes a significant increase in test cost because of much longer test time and elevated tester memory requirements to store the test data. Therefore test compression techniques are essential to reduce the test cost by reducing.fectively the large volume of don’t-care bits in test vectors. We also introduce modied ATPG algorithms upon the previous SCC scheme and explore various implementation strategies. Experimen-tal data exhibit signicant reductions on test time and volume over all current test compression techniques. Categories and Subject Descriptors

The overall test time will determine whether ATPG alone or combined LBIST-ATPG should be selected to test the chip. Compare and calculate the test time for Example 3 using the top-level .

These metrics generally indicate test quality (higher with more fault detections) and test application time (higher with more patterns). ATPG efficiency is another important consideration that is influenced by the fault model under consideration, the type of circuit under test (full scan, synchronous sequential, or asynchronous sequential), the . We will cover topics such as scan chains, test compression, ATPG algorithms, boundary scan, BIST architectures, and fault modeling. . reduce time-to-market, and enhance the overall quality of the manufactured chips. . allowing test vectors to be serially shifted in and out. This enables efficient and effective testing of integrated circuits.Multiple conventional Scan compression approaches are available to reduce the test time & test data volume for years & had addressed test solutions at higher technology nodes. Nonetheless, they have certain limitations to address key . Design B is a configurable coherent interconnect microarchitecture with 509K scan flops. For experimental purposes, no test compression logic is inserted for design B, and only simple scan chains are stitched. The .

data upload time, test application time, and ATE vector . Compressed ATPG Vectors, IEEE Proc. In t. Test . . Dimensional Test Data Compression for Scan-Based . Instead of modifying the ATPG procedure, some post-ATPG methods modify a given test set by using X-filling to reduce as much test power as possible [7], [10], [16] or to satisfy the power . The aim of test generation at the gate level is to verify that each logic gate in the circuit is functioning correctly, and the interconnections are good. If only a single stuck-at fault is assumed to be present in the circuit under test, then the problem is to construct a test set that will detect the fault by utilizing only the inputs and the outputs of the circuit.

atpg gate delay fault

LBIST The LBIST (Logic built in self test) is inserted into a design to generate patterns for self-testing.. JTAG/Boundary Scan Method for testing interconnects on printed circuit board or sub blocks inside an IC. JTAG developed a specification for boundary scan testing that was standardized in 1990. MBIST MBIS is a self testing and repair mechanism which tests the .fault diagnosis [2], [3], but the number and size of scan test vectors is steadily increasing—even for highly compacted vector sets generated with modern automatic test pattern generation (ATPG). Cost-effective test requires a form of scan compression to address the issues of increasingly com-Test set are randomly generated by Automatic Test Pattern Generation (ATPG) tool in Built-In Self-Test (BIST) architecture, which is performed on LFSR (line-ar-feedback shift-register) reseeding scheme with seed vectors, it significantly reduces test-data storage and transmission bandwidth. For given a deterministic testachieved on the transformed test set using statistical coding. ATPG algorithms for producing test vectors that can more effectively be com-pressed using statistical codes have been described in [20]. Test vector compression based on hybrid BIST techniques have been described in [10], [29], and [27]. A novel scheme of test vector compression

Two test strategies are used to test virtually all IC logic: automatic test pattern generation (ATPG) with test pattern compression and logic built-in self-test (BIST). Test Compression. Test Compression DFT technique involves compressing the amount of test data (stimulus and response) that must be stored on the Automatic Test Equipment [ATE] for testing, from the ATPG generated test-set. . The boundary scan cells provide scan paths in the form of a scan chain which provides the ability to shift-in the test .

The past decade observed compression of test data as an effective method for reducing the volume of test data and test application time. In order to work with the increasing clock frequencies in a contemporary design, a low fill rate of care bits is exploited due to the result of combinational logic [].Hence, the fill rate of the every determined test pattern did not exceed .

This paper proposes novel algorithms for computing test patterns for transition faults in combinational circuits and fully scanned sequential circuits. The algorithms are based on the principle that s@ vectors can be effectively used to construct good quality transition test sets. Several algorithms are discussed. Experimental results obtained using the new algorithms .

spigen neo hybrid galaxy s6 drop test

at speed scan test

Resultado da 410 mariana ximenes FREE videos found on XVIDEOS for this search.

atpg scan test time compression vectors|atpg scan test